# マルチ FPGA ボードを用いた OFDM 無線伝送シミュレータ An OFDM Wireless Transmission Simulator using Multi-FPGA Board

寒河江 佑太 , 須山 聡 , 鈴木 博 , 府川 和彦

# 東京工業大学 大学院理工学研究科集積システム専攻 〒152-8550 東京都目黒区大岡山 2-12-1

TEL/FAX: 03-5734-3770

e-mail: {yuta, ssuyama, suzuki, fukawa}@radio.ss.titech.ac.jp

URL: http://www.radio.ss.titech.ac.jp

# 1.はじめに

移動無線通信において DSP や FPGA などのプログラマブル・デバイスによるソフトウェア無線 (Software Defined Radio: SDR) の研究が進められている. SDR により,ソフトウェアを変更だけで異なる周波数帯域・伝送方式に対応できることが期待されている.その研究のためにはリアルタイム動作可能な無線信号処理アルゴリズムを,効率良く研究・開発できる無線伝送シミュレータが必要不可欠である.今後,信号伝送速度は1Gb/sを目標に研究が進められるので,試作・実験等を考慮すると DSP を用いたシミュレータでは不十分である [1]. 本稿では,FPGA を用いた数百Mb/sのOFDM 無線伝送シミュレータを検討したので,その概要と特性について述べる.

# 2.OFDM 無線伝送シミュレータ

#### 2.1 基本構成

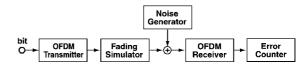

OFDM 無線伝送シミュレータに実装するモジュールの基本構成を図1に示す.送信モジュール, 受信モジュールに加え, 伝送性能を評価するために無線伝搬路モジュール, 雑音発生モジュール, ビット誤り率およびパケット誤り率の測定モジュールから構成される.

OFDM 方式のパラメータは,**表1**のように 5GHz 帯無線 LAN に準拠したものを採用する [2]. ただし,変調方式としては符号化率 1/2 の QPSK のみとする .伝送速度はクロック周波数に連動して変えられる . 送信ビット系列は FPGA 内部のPN 系列発生器により生成する . 内部のディジタル化された信号を 16 bit 固定小数点で表示する .

#### 2.2 構成モジュール

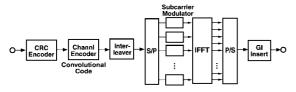

OFDM 送信処理モジュールの内部を**図2**に示す.送信ビット系列に対して畳み込み符号化・インタリーブし,各サブキャリアにおいて QPSK 変調する.さらに IFFT で時間領域の信号に変換後,ガードインターバルを挿入する.

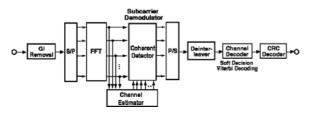

OFDM 受信処理モジュールの内部を**図3**に示す.受信信号からガードインターバルを除去し,FFT により周波数領域に変換する.各サブキャリアにおいて同期検波を行い,デインタリーブ後に

図1 無線伝送シミュレータのモジュール構成

表1 実装パラメータ

| 変調方式             | QPSK                |

|------------------|---------------------|

| FFT ポイント数        | 64                  |

| 有効キャリア数          | 52                  |

| ガードインターバル長 $T_G$ | 16 pt               |

| シンボル周期 $T_s$     | 80 pt               |

| 誤り訂正             | 畳み込み符号 (R=1/2, K=7) |

| 復号方法             | 軟判定ビタビ復号            |

| 伝搬路モデル           | 16 パス指数減衰モデル        |

図2 OFDM 送信処理モジュール

図3 OFDM 受信処理モジュール

軟判定ビタビ復号を行う.同期検波では,パイロット信号を用いて推定された伝搬路の周波数応答を用いて,各サブキャリアの振幅と位相の変動を除去している.

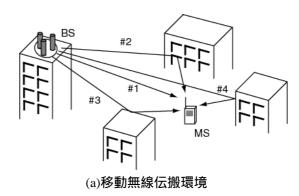

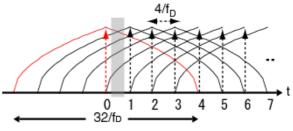

無線伝搬路モジュールでは,無線通信特有のマルチパス・フェージング環境を実現している.無線通信では,**図4**(a) のように基地局から送信された信号は建物などで反射・散乱・回析し様々な経路を通って受信され,さらに端末がそのようなフェージング環境下を移動するので,ドップラー効果により伝搬環境が時間的に変動し,いわゆるフェージングが発生する.また,高速伝送においては異なる経路の受信信号間には,経路差によって遅延時間差が生じるため,周波数選択性フェージング環境となる.このような環境をモデル化するため,同図(b)に示すように一定時間幅のパスが一定時間ごとに生成し,かつWSSUS条件を満たすアルゴリズムを用いる[3].

# 3. 実装

# 3.1 マルチ FPGA ボードの構成

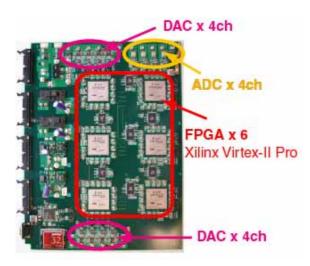

ベースバンド伝送系無線伝送シミュレータを, **図5**のマルチ FPGA 搭載ボード上に実現した 約 700 万システム・ゲートの FPGA (Xilinx 社製 Virtex- Pro: XC2VP70) を 6 個搭載している[4]. FPGA 間には,64 bit の直接結線と,2種類 (128

Maximum Doppler Frequency : fD

(b)モデル化

図4 移動無線伝搬環境のモデル化

bit, 64 bit × 2) のバス結線があり、FPGA 間のボトルネックを低減している.また、14 bit、105 Ms/s の ADC を 4 チャネル、14 bit、160 Ms/s の DAC を 8 チャネル搭載している. これらの高速・高精度 ADC により実際の高速信号を入力とする動作検証が可能である.また、DAC により FPGA 内部の信号を観測しながらデバッグが可能である. なお、送受信処理モジュールで用いる IFFF/FFT には Xilinx 社から提供されている IPコアを用いた.

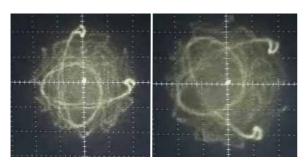

## 3.2 FPGA 内部信号の観測

DAC 出力より取得した FPGA の内部信号をオシロスコープで観測した結果を**図6**に示す .フェージング環境では , 同図 (a) のような OFDM の送信 IQ コンスタレーションが , 同図 (b) のように振幅と位相が歪んで受信される .また ,各パスの遅延時間差が大きい場合には 同図 (c) のように遅延波が多重される .このような環境下であっても , OFDM 受信機では , ガードインターバル

図5 マルチ FPGA ボード

(a) OFDM 送信信号

(b) フェージング環境

(c) 周波数選択性 フェージング環境

(d) 同期検波後の信号

図6 観測された信号

以内の遅延波であれば、同図 (d) のように送信された QPSK 信号を復元できる.

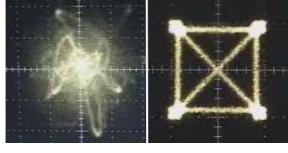

**図7** (a) と (b) に送信信号と受信信号のスペクトルを示す.同図 (b) は周波数選択性フェージング環境におけるスペクトルであり,信号帯域内に落ち込みが発生する.

上述したように,このシミュレータではFPGA

(a) 送信信号

(b) 受信信号

図7 信号の周波数特性

表2 実装モジュールの性能

| 構成要素                 | 機能・特徴                           | 最大動作速度                        |

|----------------------|---------------------------------|-------------------------------|

| 送信処理部                | QPSK 変調<br>64 ポイント IFFT         | 170 MHz<br>120 MHz            |

| 移動無線伝搬路<br>シミュレーション部 | フェージングモデル<br>ガウス雑音生成            | 120 MHz                       |

| 受信処理部                | 64 ポイント FFT<br>同期検波<br>軟判定ビタビ復号 | 120 MHz<br>170 MHz<br>115 MHz |

内部の信号を視覚的にデバックでき,直感的にかつ効率的にアルゴリズムの検討が行える.

# 4.性能・特性

### 4.1 処理性能

シミュレータの送信処理,無線伝搬路,雑音発生,受信処理の各モジュールを3個のFPGAに分割して実装した.FPGAの使用率はボード全体の10%程度であった.表2に実装した各モジュールの最大動作速度を示す.サンプリング周波数を20 MHz に設定すれば容易にIEEE 802.11 a/g の12 Mb/s QPSK変調を実現できる.実装したモジュールにおけるサンプリング周波数の上限は120 MHzであり,その場合72 Mb/s 程度のリアルタイム伝送を実現できる.そのため DSPを用いたシミュレータと比較して大幅な高速化を達成できた.また,使用ゲート・リソースにはまだかなりの余裕があることから,より高度で複雑なアルゴリズムのリアルタイム検証が可能である.

### 4.2 特性

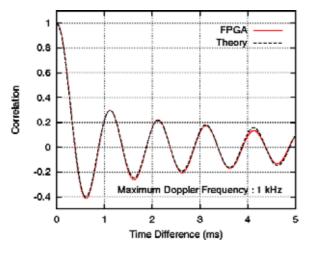

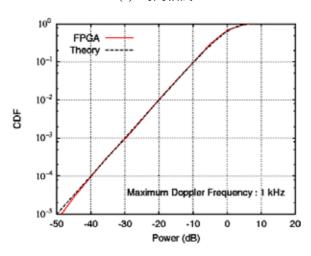

理論値 計算機シミュレーションとの特性比較を行った .図8に FPGA で生成したフェージング

(a) 時間相関

(b) 累積確率分布 図 8 無線伝搬路モジュールの特性

の (a) 時間相関, (b) パス電力の累積確率分布 (CDF) を示す.時間相関は,ほぼ理論値と一致している.累積確率分布は,電力が - 40 dB 程度まで理論値と一致しており,伝搬モデルの統計的な性質を高精度に実現している.

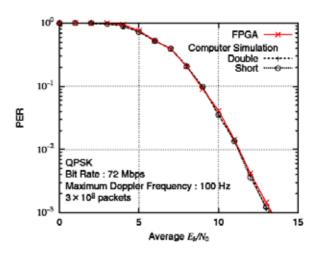

シミュレータ全体の伝送特性を表すパケット 誤り率 (PER) 特性を**図9**に示す. PER 特性は, 倍精度浮動小数点 (Double) および16 bit 固定小 数点 (Short) による計算機シミュレーション結 果とほぼ同等であり,FPGAに実装したモジュー ルが正しく動作していることを示している.

図9 パケット誤り率特性

# 5.まとめ

リアルタイム検証を行うマルチ FPGA ボードを用いた OFDM 無線伝送シミュレータを検討し、そのハードウェア構成、実装したモジュールおよび性能について示した.本シミュレータに実装した誤り訂正を含めた OFDM 伝送系の伝送速度は72 Mb/s に達することを示した.また、実装した無線伝搬路モジュールは,数学的にモデル化された環境を忠実に実現していることを示した.今後、MIMO-OFDM 伝送系、ターボ等化技術のモジュール実装、RF を含むアナログ回路の構築等を行う予定である.

# 参考文献

- [1] 小塚宣秀,須山 聡,鈴木 博,府川和彦, "マルチ DSP による OFDM 用適応等化シミュレ ータ," *信学技報*, RCS2002-283, 2003 年 3 月.

- [2] IEEE Std 802.11a, High-speed Physical Layer in the 5 GHz Band, 1999.

- [3] N. Suwunniponth, et al, "A Continuously time-varying fading model for mobile radio channels," Proc. 1999 IEEE Intern. Symp. on Intelli. Signal Proc. and Commun. Systems, pp. 137-140, Dec. 1999.

- [4] 東京エレクトロンデバイス,

http://inrevium.teldevice.co.jp/board/spp1000.html